## **FACULDADE ANHANGUERA DE SBC**

## AULA 7- Revisão para Prova P1- Profº. Cristiano Malheiro- 02/10/2017- Bons estudos!!!

## **Eletrônica Digital Sequencial**

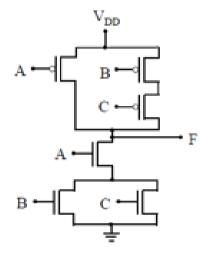

**1.** Qual a expressão lógica para o circuito CMOS abaixo (utilize mapa de karnaugh e depois o método da associação série e paralelo):

2. Obtenha o circuito por associação série e paralelo para a expressão abaixo:

$$G = \overline{A + B \cdot C + D}$$

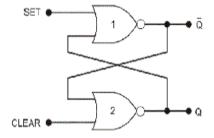

**3.** Construa a tabela expandida e reduzida com estado futuro Qn+1 para o Latch-NOR.

4. Construa o Flip- Flop RS a partir da lógica de Latch Nand. Dado a tabela reduzida RS

| R | S | Q <sub>n+1</sub> |

|---|---|------------------|

| 0 | 0 | Qn               |

| 0 | 1 | 1                |

| 1 | 0 | 0                |

| 1 | 1 | Х                |

| R | S | Qn | Q <sub>n+1</sub> |

|---|---|----|------------------|

| 0 | 0 | 0  |                  |

| 0 | 0 | 1  |                  |

| 0 | 1 | 0  |                  |

| 0 | 1 | 1  |                  |

| 1 | 0 | 0  |                  |

| 1 | 0 | 1  |                  |

| 1 | 1 | 0  |                  |

| 1 | 1 | 1  |                  |

| S | С | $Q \rightarrow Q_{n+1}$ |

|---|---|-------------------------|

| 1 | Х | 0 0                     |

| 0 | 1 | 0 1                     |

| 1 | 0 | 1 0                     |

| Х | 1 | 1 1                     |

- a. Ache a equação de estado;

- b. Obtenha a expressão para o S e para o C;

- c. Complete o circuito lógico.