#### Critérios de Avaliação

1. Avaliações:

B1 – peso 4- 1º bimestre:

- 3 pontos (laboratórios, listas e relatórios)

- 7 pontos (avaliação prevista para 07/04/2017).

$B2 - peso 6 - 2^{\circ} bimestre$ :

- 3 pontos (laboratórios, listas e relatórios)

- 7 pontos (avaliação confirmada para 09/06/2017 e 16/06/2017).

SUB – toda a matéria (Substitui a menor nota):

- 10 pontos (avaliação prevista para 23/06/2017).

- \*\*\*Datas de acordo com calendário acadêmico!!!

#### PLD D2-115 da Altera

#### O que é um PLD?

É um **dispositivo lógico programável** (*Programmable logic device* - PLD) utilizado para construir <u>circuitos digitais</u>.

Ao contrário de uma <u>porta lógica</u>, que tem uma função fixa, um PLD tem uma função indefinida quanto a sua fabricação. Antes de se utilizar um PLD num circuito, este deve ser programado (via linguagem ou via esquemático).

kroton

## Aula 8- Lab

#### PLD D2-115 da Altera

#### Como o PLD guarda a configuração?

Um PLD é uma combinação de dispositivos lógicos e de memória. A memória é usada para guardar o padrão que é dado ao chip durante a programação. Muitos dos métodos para armazenar dados no circuito integrado foram adaptados para serem usados em PLDs. Isto inclui:

**SRAM**

Células EPROM, EEPROM

Memória Flash

PLDs baseadas em SRAM tem que ser programadas cada vez que a energia é ligada isto normalmente é feito por outra parte do circuito. Uma célula EPROM é um transistor MOS (semicondutor de óxido metálico) que pode ser comutada por uma carga eléctrica permanente aplicada no seu eletrodo 'gate'. Uma memória FLASH é não-volátil, retendo a informação mesmo que a energia elétrica seja desligada.

#### PLD D2-115 da Altera

## Aula 8- Lab

# PLD D2-115 da Altera

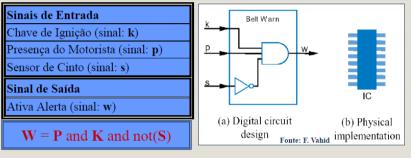

Questão: Como transformar o projeto de um sistema digital (normalmente representado por um desenho contendo um conjunto de símbolos lógicos interligados) em um circuito físico real, implementado com Circuitos Integrados (CI's)?

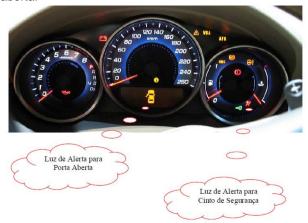

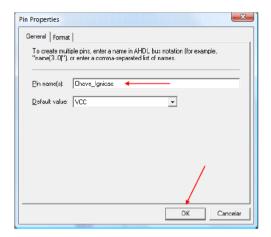

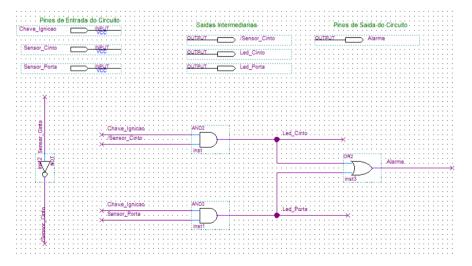

Utilizaremos como exemplo o circuito lógico de alerta de abertura do cinto de segurança, representado na figura seguinte.

#### Aula 8- Lab

**PLD** (*Programmable Logical Devices*) caracterizam-se por permitir ao projetista configurar as células lógicas do CI de modo adequado a atender ao projeto, sem a necessidade de fabricação de componentes especiais.

#### Tipos de PLD:

- SPLD (Simple Programmable Logic Devices): circuitos com centenas de portas lógicas básicas (AND e OR) e eventualmente registradores, que podem ser interconectadas pelo projetista através de ferramentas de configuração de hardware:

- CPLD (Complex Programmable Logic Devices): circuitos com centenas de elementos lógicos (cada um deles similar a um SPLD), que podem ser configurados individualmente e interconectados pelo projetista através de ferramentas de configuração de hardware;

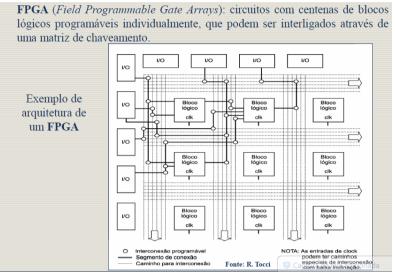

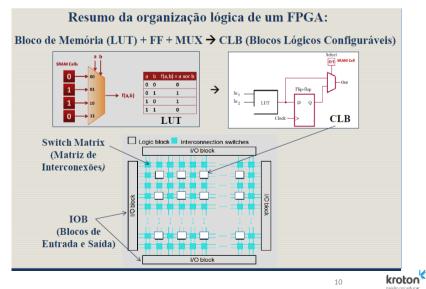

- FPGA (Field Programmable Gate Arrays): circuitos com centenas de blocos lógicos programáveis individualmente, através de blocos de memória (tabelas de consulta), que podem ser interligados através de uma matriz de chaveamento, também programável pelo projetista através de ferramentas de configuração de hardware.

**Kroton**

\* Pág. 486 TOCCI, 11ª edição

## Aula 8- Lab

5

## Aula 8- Lab

#### O Projeto

Sistema simples de alarme de automóvel para detectar, quando a Chave de Ignição está ligada, se o Cinto de Segurança não está afivelado ou uma das Portas está aberta.

#### Passo a passo

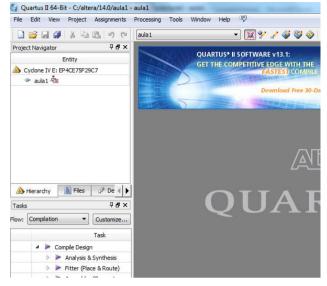

#### Iniciar um Novo Projeto

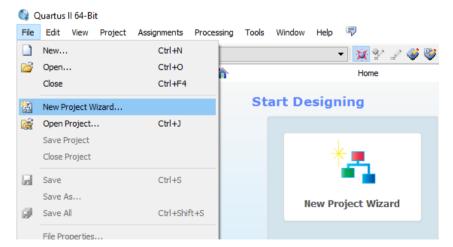

Para começar a trabalhar em um projeto novo, primeiro temos que definir um escopo para este projeto. O "software" Quartus II facilita esta tarefa fornecendo suporte na forma de um Assistente ("Wizard"). A criação de um Novo Projeto segue as etapas detalhadas a seguir.

- a) Selecionar **File > New Project Wizard** para iniciar o Assistente de Novo Projeto o qual direciona a criação e configurações preliminares de um Novo Projeto.

- b) Na janela "New Project Wizard: Introduction", clicar em Next.

13

## Aula 8- Lab

Janela "New Project Wizard: Add Files". O Assistente de Novo Projeto permite incluir arquivos pré-existentes (se houver) no Projeto.

#### Aula 8- Lab

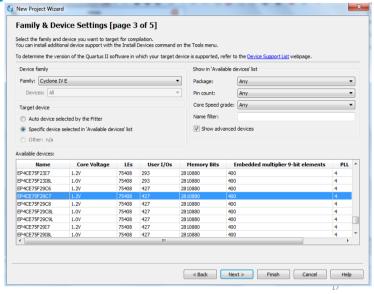

Na janela "New Project Wizard: Family & Device Settings":

f.1) Especificar o tipo de dispositivo no qual o circuito projetado será implementado.

No campo "Device Family – Family:", escolher Ciclone IVE como Família do dispositivo de destino.

f.2) Pode-se deixar o "**software" Quartus II** selecionar um dispositivo específico na família, ou podemos escolher o dispositivo explicitamente. Utilizaremos esta última abordagem

No campo "Target device" escolher a opção "Specific device selected in 'Available devices' list".

f.3) No campo "Available devices" aparece uma lista de dispositivos disponíveis, escolher o dispositivo denominado EP2C70F896C6 que é um PLD utilizado na Placa Didática de Desenvolvimen

kroton<sup>⊀</sup>

## Aula 8- Lab

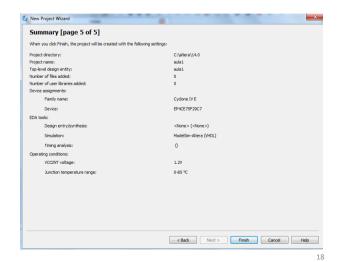

Resumo das Configurações escolhidas:

9

## Aula 8- Lab

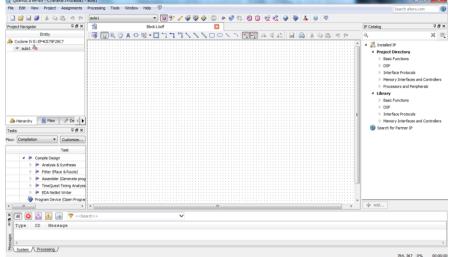

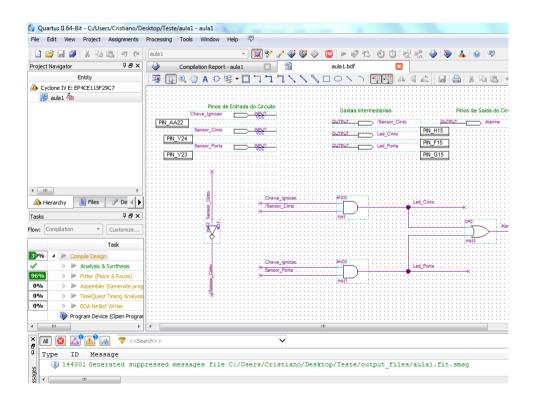

Para descrever o circuito no formato de Captura de Esquemático deve-se usar o Editor Gráfico do Quartus II, conforme as etapas detalhadas a seguir.

a) Selecionar File > New para obter a janela da Figura 14. Escolher "Block Diagram / Schematic File" e clicar em OK. Isso abre a janela do Editor Gráfico (Figura 15).

## Aula 8- Lab

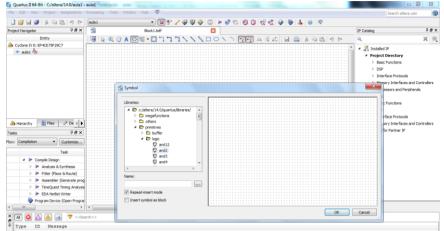

O Editor Gráfico oferece uma série de bibliotecas que incluem elementos de circuito que podem ser importados para um esquemático. Dê um duplo clique no espaço em branco na janela do Editor Gráfico, ou clique no ícone na barra de ferramentas que se parece com uma porta AND .

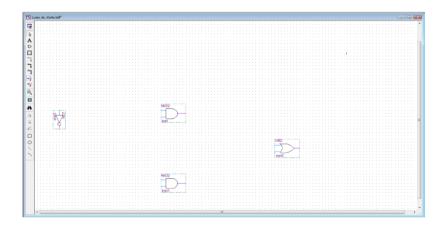

Vá em "libraries", em seguida, expandir a biblioteca "primitives", seguido de expansão da biblioteca "logic" que compreende as portas lógicas. Selecione "and2", que é uma Porta E de duas entradas, e clique em OK. Agora, o símbolo da Porta E aparecerá na janela do Editor Gráfico. Usando o mouse, mova o símbolo para um local conveniente e clique para colocá-lo lá. Importar a segunda

kroton

23

# Aula 8- Lab

Figura 20 Importar os símbolos das Portas Lógicas e organizá-los na janela do Editor Gráfico.

Vamos acrescentar três saídas intermediárias no circuito!!!

25

# Aula 8- Lab

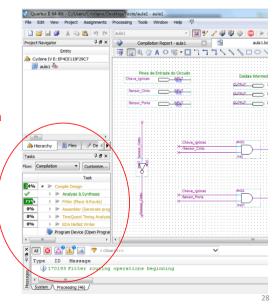

#### Compilar o Circuito Projetado

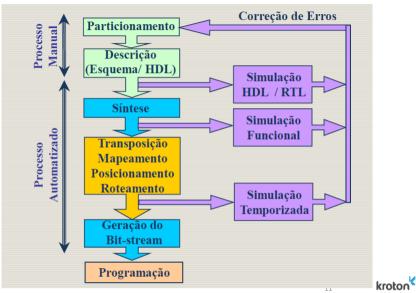

O arquivo do diagrama esquemático descrito – Luzes\_de\_Alerta.bdf, será processado por várias ferramentas do Quartus II que irão analisar o arquivo, sintetizar o circuito, e gerar uma implementação deste circuito para o chip de destino. Estas ferramentas são controladas pelo programa aplicativo chamado **Compilador.**

Para executar o Compilador selecionar **Processing > Start Compilation**, ou clicar no ícone da barra de ferramentas horizontal.

À medida que a compilação passa pelos vários estágios, seu progresso é relatado em uma janela no lado esquerdo da tela do Quartus II (janela "Tasks"). O sucesso (ou insucesso) do processo de compilação é indicado em uma caixa de diálogo,

kroton

## Aula 8- Lab

## Simulação

Aparece status na janela Tasks!!

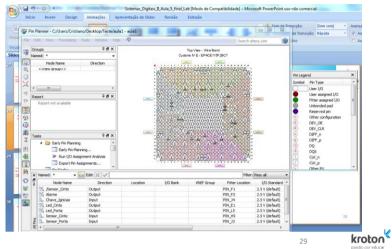

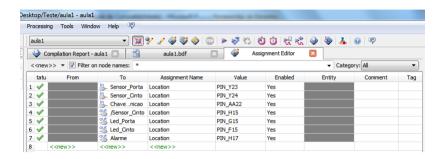

#### Atribuição de Pinos do PLD

#### Assignments > Pin Planner

# Aula 8- Lab

Atribuição de Pinos do PLD

Assignments > Pin Planner

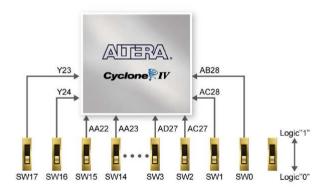

Figure 4-8 Connections between the slide switches and Cyclone IV E FPGA

Kroton

Table 4-1 Pin Assignments for Slide Switches

| Signal Name | FPGA Pin No. | Description      | I/O Standard     |

|-------------|--------------|------------------|------------------|

| SW[0]       | PIN_AB28     | Slide Switch[0]  | Depending on JP7 |

| SW[1]       | PIN_AC28     | Slide Switch[1]  | Depending on JP7 |

| SW[2]       | PIN_AC27     | Slide Switch[2]  | Depending on JP7 |

| SW[3]       | PIN_AD27     | Slide Switch[3]  | Depending on JP7 |

| SW[4]       | PIN_AB27     | Slide Switch[4]  | Depending on JP7 |

| SW[5]       | PIN_AC26     | Slide Switch[5]  | Depending on JP7 |

| SW[6]       | PIN_AD26     | Slide Switch[6]  | Depending on JP7 |

| SW[7]       | PIN_AB26     | Slide Switch[7]  | Depending on JP7 |

| SW[8]       | PIN_AC25     | Slide Switch[8]  | Depending on JP7 |

| SW[9]       | PIN_AB25     | Slide Switch[9]  | Depending on JP7 |

| SW[10]      | PIN_AC24     | Slide Switch[10] | Depending on JP7 |

| SW[11]      | PIN_AB24     | Slide Switch[11] | Depending on JP7 |

| SW[12]      | PIN_AB23     | Slide Switch[12] | Depending on JP7 |

| SW[13]      | PIN_AA24     | Slide Switch[13] | Depending on JP7 |

| SW[14]      | PIN_AA23     | Slide Switch[14] | Depending on JP7 |

| SW[15]      | PIN_AA22     | Slide Switch[15] | Depending on JP7 |

| SW[16]      | PIN_Y24      | Slide Switch[16] | Depending on JP7 |

| SW[17]      | PIN_Y23      | Slide Switch[17] | Depending on JP7 |

31

# Aula 8- Lab

Table 4-3 Pin Assignments for LEDs

| Table 4-3 Pin | Assignments for LEI | Os          |              |

|---------------|---------------------|-------------|--------------|

| Signal Name   | FPGA Pin No.        | Description | I/O Standard |

| LEDR[0]       | PIN_G19             | LED Red[0]  | 2.5V         |

| LEDR[1]       | PIN_F19             | LED Red[1]  | 2.5V         |

| LEDR[2]       | PIN_E19             | LED Red[2]  | 2.5V         |

| LEDR[3]       | PIN_F21             | LED Red[3]  | 2.5V         |

| LEDR[4]       | PIN_F18             | LED Red[4]  | 2.5V         |

| LEDR[5]       | PIN_E18             | LED Red[5]  | 2.5V         |

| LEDR[6]       | PIN_J19             | LED Red[6]  | 2.5V         |

| LEDR[7]       | PIN_H19             | LED Red[7]  | 2.5V         |

| LEDR[8]       | PIN_J17             | LED Red[8]  | 2.5V         |

| LEDR[9]       | PIN_G17             | LED Red[9]  | 2.5V         |

| LEDR[10]      | PIN_J15             | LED Red[10] | 2.5V         |

| LEDR[11]      | PIN_H16             | LED Red[11] | 2.5V         |

| LEDR[12]      | PIN_J16             | LED Red[12] | 2.5V         |

| LEDR[13]      | PIN_H17             | LED Red[13] | 2.5V         |

| LEDR[14] | PIN_F15 | LED Red[14]  | 2.5V |  |  |  |

|----------|---------|--------------|------|--|--|--|

| LEDR[15] | PIN_G15 | LED Red[15]  | 2.5V |  |  |  |

| LEDR[16] | PIN_G16 | LED Red[16]  | 2.5V |  |  |  |

| LEDR[17] | PIN_H15 | LED Red[17]  | 2.5V |  |  |  |

| LEDG[0]  | PIN_E21 | LED Green[0] | 2.5V |  |  |  |

| LEDG[1]  | PIN_E22 | LED Green[1] | 2.5V |  |  |  |

| LEDG[2]  | PIN_E25 | LED Green[2] | 2.5V |  |  |  |

| LEDG[3]  | PIN_E24 | LED Green[3] | 2.5V |  |  |  |

| LEDG[4]  | PIN_H21 | LED Green[4] | 2.5V |  |  |  |

| LEDG[5]  | PIN_G20 | LED Green[5] | 2.5V |  |  |  |

| LEDG[6]  | PIN_G22 | LED Green[6] | 2.5V |  |  |  |

| LEDG[7]  | PIN_G21 | LED Green[7] | 2.5V |  |  |  |

| LEDG[8]  | PIN_F17 | LED Green[8] | 2.5V |  |  |  |

33

#### Atribuição de Pinos do PLD

#### Assignments > Assignment Editor

kroton

35

## Aula 8- Lab

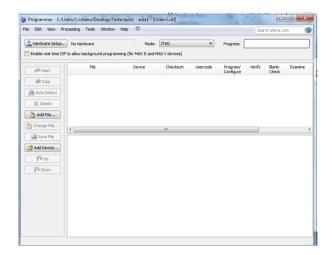

## Programação do PLD

Vá em Tools > Programmer > Hardware Setup > USB- Blaster [USB-0] e add o arquivo. sof

#### Programação do PLD

#### Após isso clique em start e acompanhe o progresso

## Aula 8- Lab

Através das chaves e LEDs, testar o circuito projetado e programado no PLD, completando a Tabela Verdade abaixo:

| Variáveis de Entrada |              |              | Variáveis de Saída |           |           |        |

|----------------------|--------------|--------------|--------------------|-----------|-----------|--------|

| SW17                 | SW16         | SW15         | LEDR17             | LEDR15    | LEDR14    | LEDR13 |

| Chave_Ignição        | Sensor_Porta | Sensor_Cinto | /Sensor_Cinto      | LED_Porta | LED_Cinto | Alarme |

| 0                    | 0            | 0            |                    |           |           |        |

| 0                    | 0            | 1            |                    |           |           |        |

| 0                    | 1            | 0            |                    |           |           |        |

| 0                    | 1            | 1            |                    |           |           |        |

| 1                    | 0            | 0            |                    |           |           |        |

| 1                    | 0            | 1            |                    |           |           |        |

| 1                    | 1            | 0            |                    |           |           |        |

| 1                    | 1            | 1            |                    |           |           |        |